文章目录 一、传输速率二、网口标准选择三、核功能选择四、共享逻辑五、总结(重点) 学习不能稀里糊涂,要学会多思考,发散式学习以及总结: FPGA作为一种器件,只是实现目的的一种方法,过度追求实现的技术细节(用hdl还是

选择Ethernet下的“1G/2.5G Ethernet PCS/PMA or SGMII”IP核

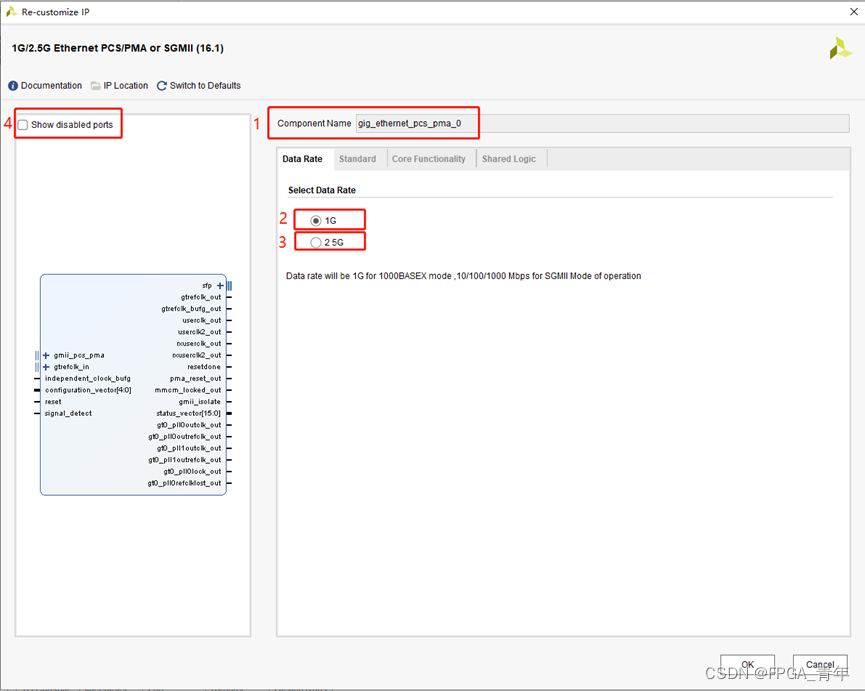

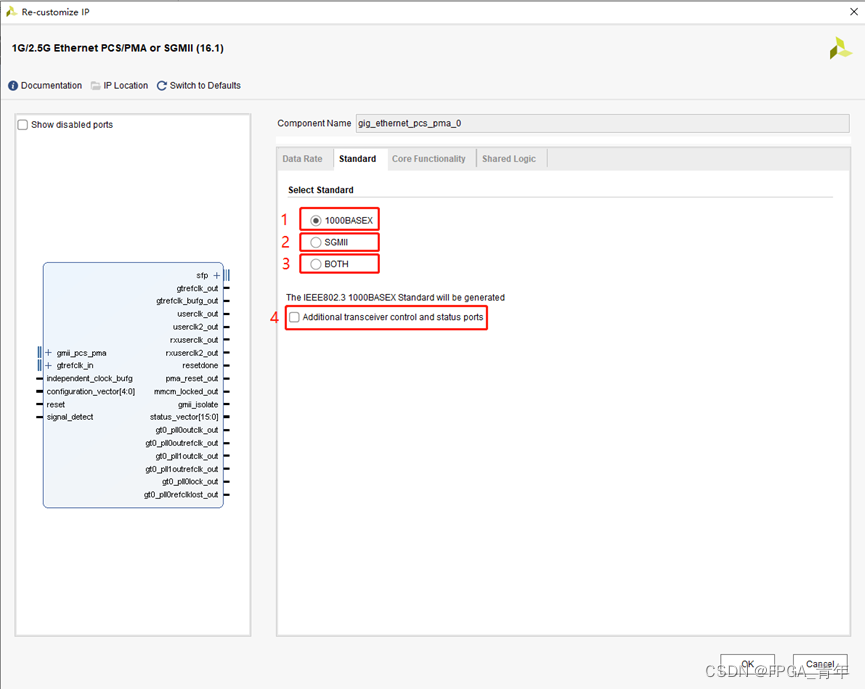

IP核配置

1:IP核的名字;

4:点击是否展开所有引脚(没必要点击);

2、3:IP核提供了两种数据速率1GMbps和2.5Gmbps,选择1G;

该IP提供了用于生成1000BASE-X,2500BASE-X,1G SGMII和2.5G SGMII四种标准应用。关于选择BASEX还是SGMII我们需要根据我们实际应用的接口选择;在这里我们参考该IP核文档pg047中的介绍:

查找文档以及使用方法可以参考这篇文章:

vivado的DocNav学习;FPGA芯片外挂DDR个数_FPGA_青年的博客-CSDN博客

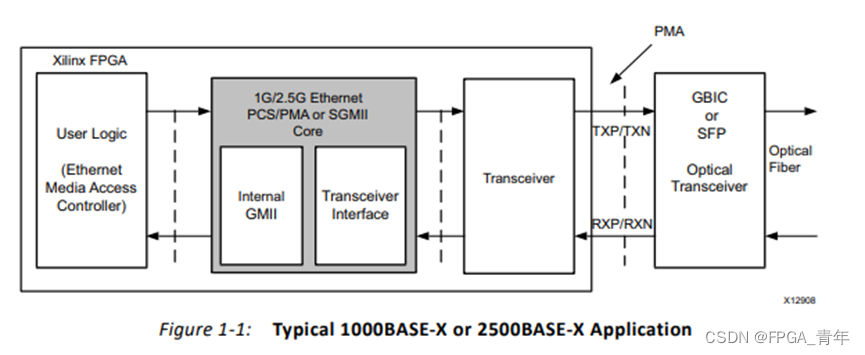

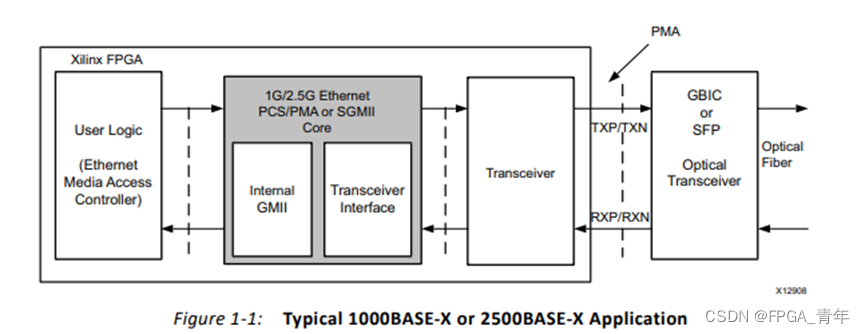

1)、(figure1-1)设备专用GT收发器支持PMA连接到外部现成的千兆接口转换器 (GBIC) 或小型可插拔 (SFP) 光收发器,以完成以太网端口,BASEX只能连接这两种器件(本次设计使用GBIC )。这里可以理解为Mac层+PCS层+PMA层以串型的方式与PHY层的PMD相连,TX/RX分别为从PMA到PMD的串行传输的差分输出,从PMD到PMA的串行传输的差分输入。

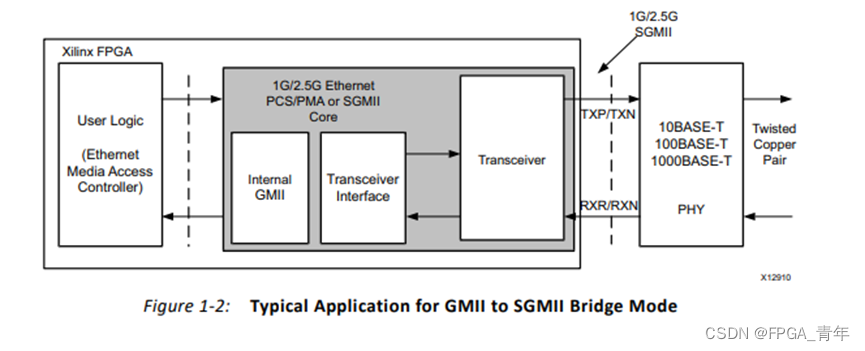

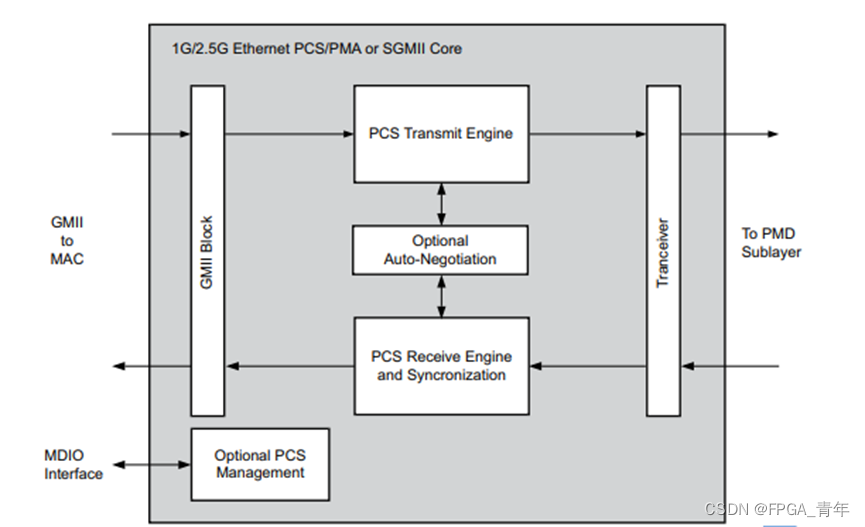

2)、(figure1-2)设备专用GT收发器也支持1g或2.5G SGMII连接到外部现成以太网PHY设备(RJ-45电口)。它也能为1G提供三模式PHY芯片的10BASE-T, 100BASE-T, and 1000BASE-T。

SGMII本质上并没有对以太网协议的分层做改动,还是MAC层,PCS层和PMA层。原来GMII模式下,MAC层一般做在FPGA侧,PHY层包括PCS+PMA做在另一个单独的芯片上。而SGMII的实施是将PCS层也同时放在了原来的MAC侧。这样FPGA芯片和PHY芯片各有一个PCS层。

对于FPGA发送来说,数据包有MAC层过来,经过TX的PCS,从SGMII接口发送出去。在PHY芯片上,有一个RX的PCS先将SGMII的信号解出GMII信号,然后再经过传统的PHY层处理发送到介质上。对于FPGA接收来说,则反过来。

关于PHY层的知识,大家可以参考此文章。

以太网学习之MAC与PHY间通信_FPGA_青年的博客-CSDN博客

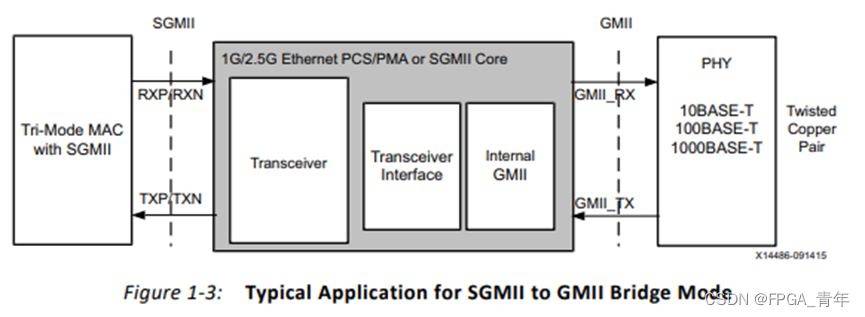

3)、(figure1-3)它也可以作为三速以太网(Tri Mode Ethernet MAC)IP核SGMII转换成GMII的桥梁。

1:1000BASEX:将生成IEE802.3 1000BASEX的标准,是千兆以太网光口的物理接口命名,属于物理层接口,可以称为物理相关接口,1000BASEX只支持1000速率,后缀BASE不持支自协商;采用光口(SFP)作为网络接口时使用( 本次设计我们选择1000BASEX );

2:SGMII:将生成GMII到Serial-GMII(SGMII)桥;可以称为媒体独立接口,SGMII支持10/100/1000速率,可以根据实际进行自协商速率转换,采用电口(RJ45)或是需要转换成GMII等信号时使用;

3:BOTH:在1000BASE-X和SGMIL标准之间进行动态切换,哪个稳定先与哪个建立连接;

4:附加收发器控制和状态端口;(暂时没有用到附加端口,不选择)

补充:

在编写代码的时候,是在用户端即上图中的User Logic处编写代码,中间为IP核内部逻辑不用管,右侧为外接接口,需要上板测试的时候需要分配此引脚(RX、TX等)。

1000表示千兆速率,base表示基带传输,X表示采用了8B/10B分组码编码方式,详细介绍可以看上一篇文章的第三部分内容:

FPGA平台以太网学习:涉及1G/2.5G Ethernet 和Tri Mode Ethernet MAC两个IP核的学习记录(一)——知识补给_FPGA_青年的博客-CSDN博客。

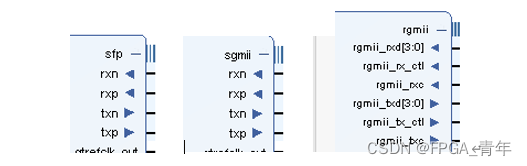

在下图中,左图是选择1000BASEX产生的外接接口SFP,中间图为选择SGMII产生的外接接口sgmii,最右边的是三速以太网IP(Tri Mode Ethernet MAC)的RGMII接口(还可以更换成GMII/MII/Internal),后边将会讲解三速以太网,到时候可以对比学习;

我们可以看到1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核采用的是RXN,RXP,TXN,TXP差分串行数据接口,此IP核采用的是FPGA芯片的GT(Gigabit Transceiver )高速收发器作为千兆网通信对外的接口。(关于GT高速收发器的知识后续有时间整理)大家可以在此大佬的文章进行学习:

Xilinx FPGA平台GTX简易使用教程(汇总篇)_fpga gtx_子墨祭的博客-CSDN博客

采用1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核时:

1、 FPGA相当于MAC层+PCS层+PMA层(属于PHY层中的一部分,选择1000BASEX);

2、 FPGA相当于MAC层+PCS层(属于PHY层的一部分,选择SGMII)。

在这里我补充一下:我们的数据在数据链路层(MAC)进行数据组帧以后,都需要经过编码PCS层和串并转换PMA层,SGMII接口属于串型接口,因此它只需要经过PCS层。

关于PHY芯片内部协议以及GT收发器的PCS和PMA可以参考这个文章:

FPGA平台以太网学习:MAC与PHY间通信_FPGA_青年的博客-CSDN博客

采用Tri Mode Ethernet MAC以太网IP核时:

1、 FPGA只是MAC层。

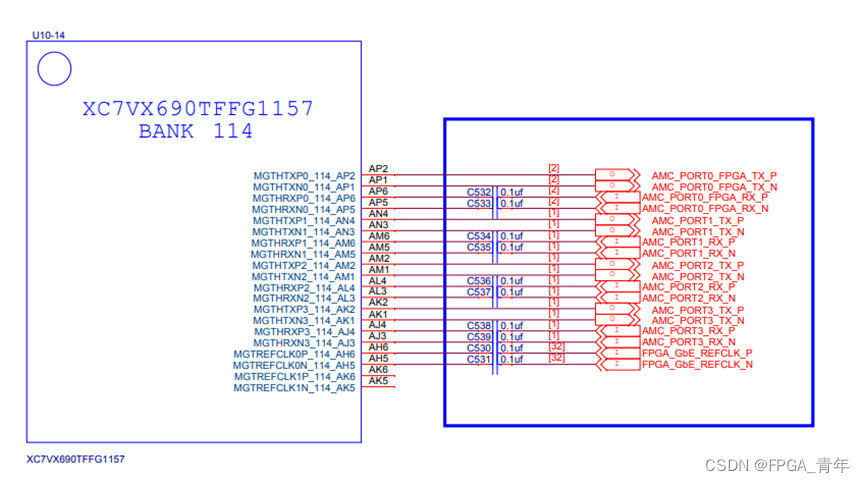

可以看下采用1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核实际用到的原理图接口,下图中共有4对高速接口port0-port3:

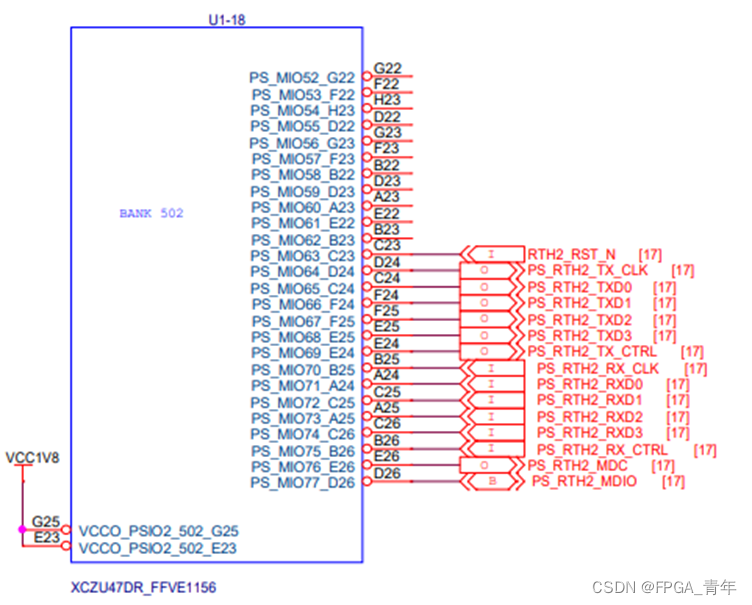

可以看下采用zynq系列时ps端进行千兆网通信的原理引脚图,Tri Mode Ethernet MAC IP核使用到的引脚同样如此。采用RGMII接口。

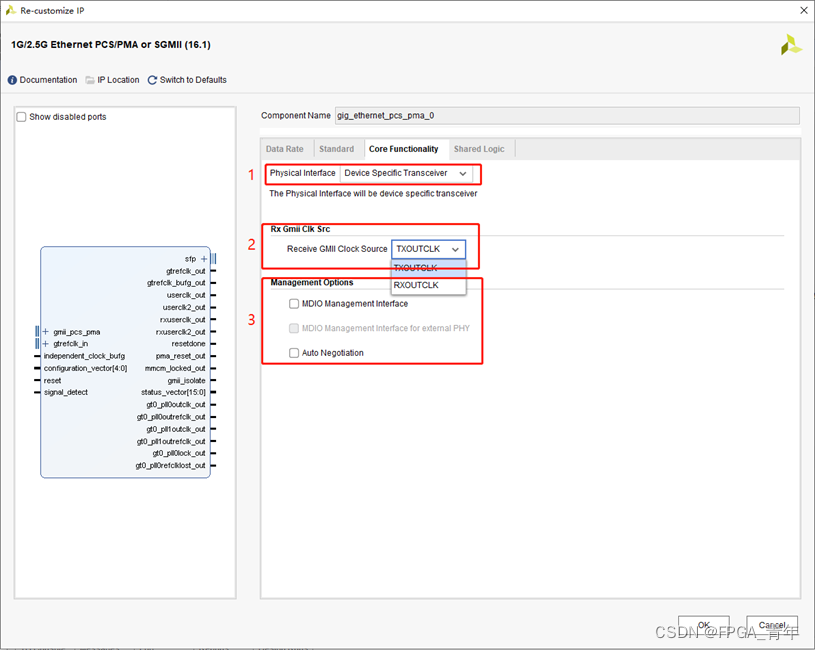

1: 物理接口:设备专用收发器;物理接口将是设备特定的收发器即GT高速收发器,即上边原理图的RT与TX(此处只有一个选项默认);

2:接收GMII时钟源:输入IP核内部的MMCM的时钟源选择为GT收发器输出的时钟TXOUTCLK(默认选项即可),该MMCM将产生我们所需要的接口时钟;

3:管理选项:MDio管理接口和自协商,这里提一下,采用SGMII外接PHY芯片时候,MDIO是为了配置PHY芯片用的,一般PHY默认配置就可以正常使用(暂时都用不到,不选);可以参考下官方的回答

以太网IP核1G/2.5G Ethernet PCS/PMA or SGMII的问题咨询 (xilinx.com)

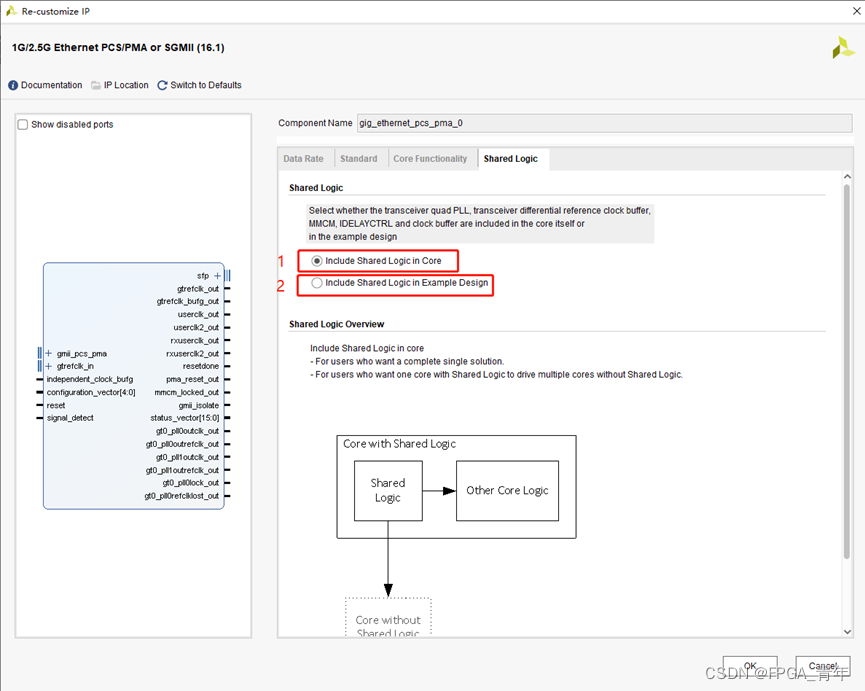

1:核内共享逻辑:设计只采用一个该IP核的时候,就选择此项

2:示例设计中包含共享逻辑:当设计中需要同时使用若干个此IP核,且所使用的GTX均位于同一个GTX BANK中,只需其中1个IP核内部的共享资源(MMCM、GTX PLL、GTX 参考时钟等)便可以满足所有IP核的需求,即选择将共享资源包含在IP核内部。通过共享逻辑可以较小硬件资源的消耗,并且各个接口输出时序是一致的。(暂时没有用到,不选)

在此IP核的配置就结束了,后边将讨论以太网应用中的设计方案

再次强调下,FPGA是工具,要学会使用工具就要看配套资料,IP配置以及接口使用在文档中讲解的都很清楚,不过都是英文的,以下链接简单介绍如何查找文档

vivado的DocNav学习;FPGA芯片外挂DDR个数_FPGA_青年的博客-CSDN博客

关于网口选择部分,我写的挺多的,主要这里边涵盖的知识非常多。主要是想说的时,在做千兆网的时候,FPGA通常采用两种外界接口。

1、一种就是普通接口MII/RMII/GMII/RGMII这些接口,RGMII是最常用的接口,这些接口都属于低速接口。例如上边介绍的ZYNQ的PS端以太网和三速以太网Tri Mode Ethernet MAC IP核这两种都是使用RGMII,与外部PHY芯片进行连接,然后再通过网口。即:FPGA=MAC<–>PHY<–>RG45。

2、还有一种就是采用高速收发器即GT接口作为外接接口,外部接的是TXP/TXN和RXP/RXN这种串型接口,上边普通的采用的是并行接口。GT用于千兆以太网物理编码子层/物理介质连接子层 (Physical coding Sublayer/Physical Media Dependent PCS/PMA)。

例如本次使用的1G/2.5G Ethernet PCS/PMA or SGMII IP核。这个IP是将PHY芯片的的PMA层和PCS层集合到了FPGA中。即FPGA=MAC+ PCS / PMA。

(1)当采用1000BASEX时候,IP核作为PCS层(编码)+PMA层(并转串),通过收发器向PMD发送,此时FPGA与外部千兆接口转换器 (GBIC) 或小型可插拔 (SFP) 光收发器进行连接。如下图所示:

(2)当采用SGMII时候,IP核作为PCS层,通过收发器向PHY芯片的PCS层发送,此时FPGA与现成以太网PHY设备(RJ-45电口)进行连接。如下图所示:

下一节,将会做接口与框架介绍。

记录美好学习,从总结开始;💪

来源地址:https://blog.csdn.net/weixin_46152123/article/details/129404990

--结束END--

本文标题: FPGA平台以太网学习:涉及1G/2.5G Ethernet 和Tri Mode Ethernet MAC两个IP核的学习记录(二)——IP学习使用

本文链接: https://lsjlt.com/news/371679.html(转载时请注明来源链接)

有问题或投稿请发送至: 邮箱/279061341@qq.com QQ/279061341

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

2024-05-24

回答

回答

回答

回答

回答

回答

回答

回答

回答

回答

0