Python 官方文档:入门教程 => 点击学习

基于C66x的内核处理器主要具有两种DMA传输:IDMA、EDMA3。IDMA:只提供核内部(L1P、L1D、L2、CFG)的数据移动服务。EDMA3:实现器件上两个存储器映射的从终端(Slave Endpoint)之间的数据传输(如DDR

基于C66x的内核处理器主要具有两种DMA传输:IDMA、EDMA3。

IDMA:只提供核内部(L1P、L1D、L2、CFG)的数据移动服务。

EDMA3:实现器件上两个存储器映射的从终端(Slave Endpoint)之间的数据传输(如DDR3、MSM SRAM、L2)。

EDMA3控制器由用户设定,服务于器件上两个存储器映射的从终端之间的数据传输;服务于软件驱动的页传输(例如,在外部存储器和内部存储器之间),执行分解或子帧取出多种数据结构,服务事件驱动的外围设备并减轻器件CPU数据传输任务。

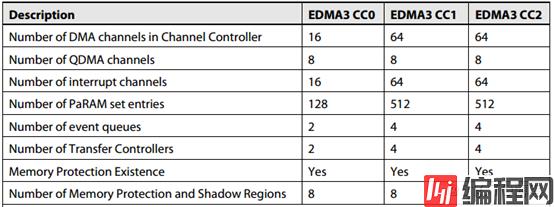

C6678处理器中,IDMA具有两个通道,EDMA具有三个通道控制器(CC0、CC1、CC2)和10个传输控制器(CC0TC0、CC0TC1,CC1TC0、CC1TC1、CC1TC2、CC1TC3,CC2TC0、CC2TC1、CC2TC2、CC2TC3)。

如图2-1所示,CC0有16个DMA通道,8个QDMA通道,16个中断通道,2个事件队列,2个传输控制TC;CC1有64个DMA通道,8个QDMA通道,64个中断通道,4个事件队列,4个传输控制TC;CC2有64个DMA通道,8个QDMA通道,64个中断通道,4个事件队列,4个传输控制TC。

图2-1 EDMA3 CC资源图

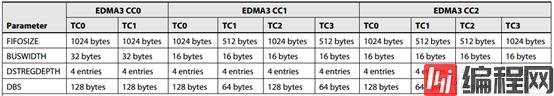

每个TC的资源情况如图2-2所示。

图2-2 EDMA3 TC资源图

CC0被优化用于内部MSMC(Multicore Shared Memory Controller)和DDR3子系统之间的数据传输,CC1、CC2被用作系统外围设备和在系统存储器间移动数据等其他传输。

每个CC有两种通道类型:DMA通道和QDMA通道。每个通道与一个给定的事件队列、传输控制器相关,并与一个给定的PaRAM参数集相关。

DMA通道和QDMA通道的主要区别在于传输是如何被系统触发的。

DMA通道传输必需一个触发事件。QDMA通道传输只需设定好触发字即可自动触发。

每个事件队列深度是16,同一时刻最多支持16个传输事件。

每个DMA、QDMA通道分配到的事件队列是可编程的。

如果在不同的通道上,事件同时被检测,事件队列会基于一个固定优先级仲裁机制仲裁。DMA通道具有比QDMA通道更高的优先级。最小编号的通道最有最高优先级。

每个事件在事件队列中按照FIFO顺序被处理。

DMA、QDMA的channel可以统一一起连续编号,TI就是如此处理的。

Global Region和Shadow Region的区别:当使用Global Region配置EDMA时,所有内核都会响应;当使用Shadow Region时,通过DRAE/DRAEH(对于DMA)和QRAE/QRAEH(对于QDMA)寄存器将不想触发的事件屏蔽,这样即使系统中的事件触发了,Shadow Region中对应的事件也不会触发。当使用global region配置EDMA时,所有的core都会响应,这样就存在某些core不想使用的event也会被触发,如果使用shadow region,通过DRE/DREH将不想触发的event屏蔽,这样即便系统中对应的event触发了,shadow region中的event也不会触发。

--结束END--

本文标题: EDMA3浅析

本文链接: https://lsjlt.com/news/186206.html(转载时请注明来源链接)

有问题或投稿请发送至: 邮箱/279061341@qq.com QQ/279061341

2024-03-01

2024-03-01

2024-03-01

2024-02-29

2024-02-29

2024-02-29

2024-02-29

2024-02-29

2024-02-29

2024-02-29

回答

回答

回答

回答

回答

回答

回答

回答

回答

回答

0